# Linear IC Converter CMOS A/D Converter (With 24-Channel Input at 10-bit Resolution)

# MB88111

# DESCRIPTION

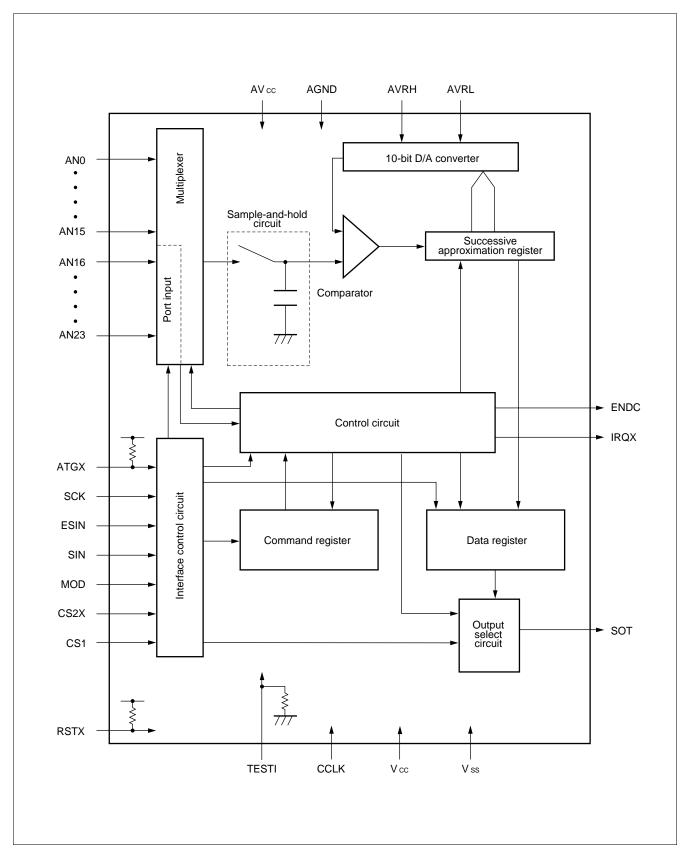

The MB88111 is an analog-to-digital converter that converts its analog input to a 10-bit digital value and outputs it as serial data.

The MB88111 employs a successive approximation method for A/D conversion. It has 24 input channels to be A/D converted selectively by setting in an internal register.

Since the MB88111 can input and output 16-bit serial data in synchronization with the clock, it can be easily connected to the serial I/O port in a 16-bit microcontroller.

### FEATURES

- 24-channel analog input

- · RC-type successive approximation system with a sample-and-hole circuit

- 10-bit resolution

- Conversion speed within 50 μs (at a system clock rate of 1 MHz)

- · Digitally converted data output from the MSB

- · Digitally converted data output as 16-bit serial data

- · Clock-synchronous serial transfer system

- Internal extended serial interface

- Capable of triggering A/D conversion through an external pin

- · Capable of input through an 8-channel port

- Serial data output format selectable using an external pin

- 10-bit monotonicity

- · No missing code

- Power supply voltage ranging from 3.5 to 5.5 V

(Continued)

### PACKAGES

(Continued)

- Operating temperature ranging from -40 to +50°C

- CMOS process

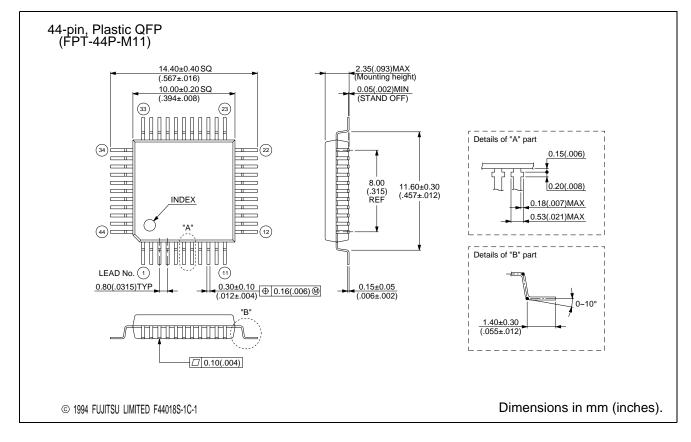

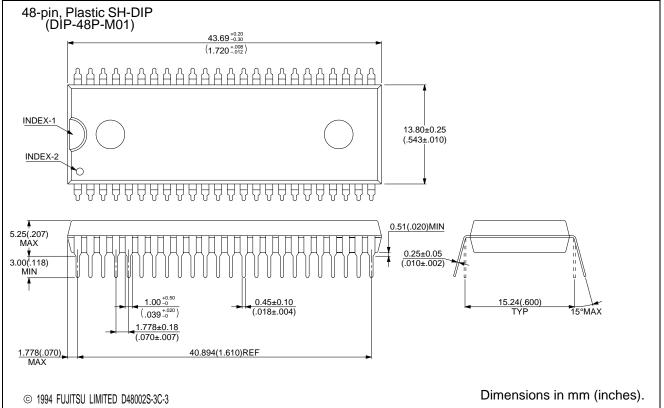

- Package options of 44-pin QFP and 48-pin SH-DIP

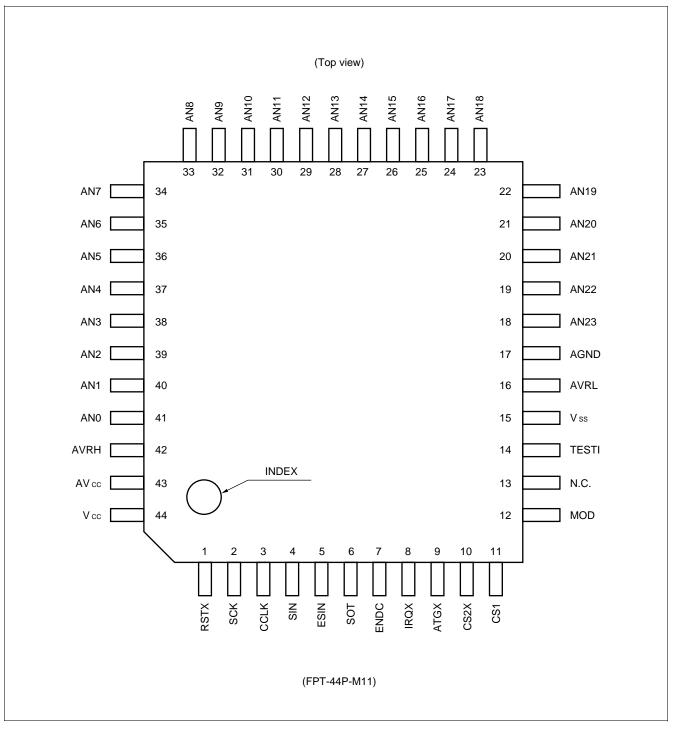

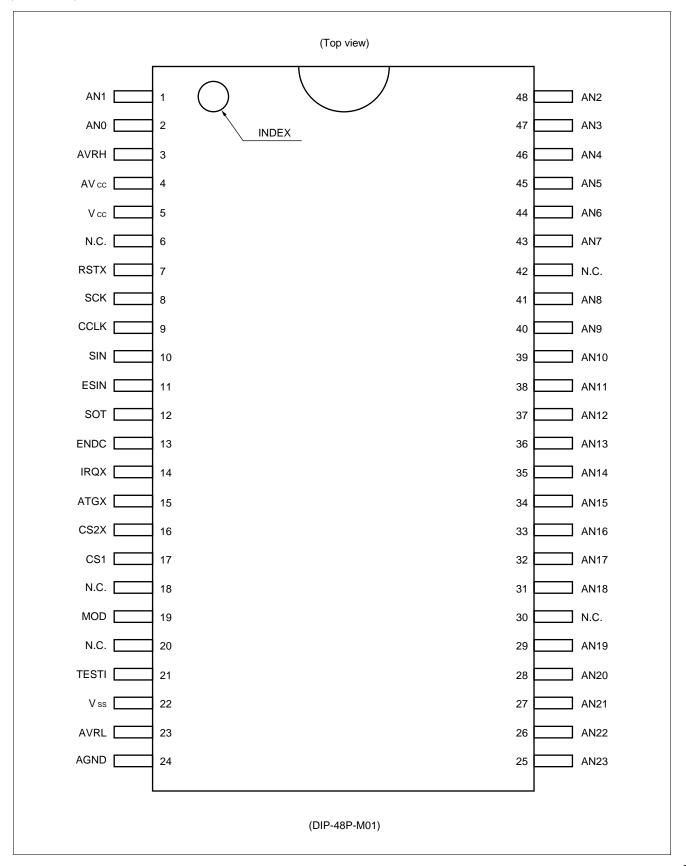

# ■ PIN ASSIGNMENT

(Continued)

#### (Continued)

# ■ PIN DESCRIPTION

| Pin      | no.                              |                 |     |              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|----------------------------------|-----------------|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP      | DIP                              | Symbol          | I/O | Circuit type | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 41 to 26 | 2 to 1,<br>48 to 43,<br>41 to 34 | AN0 to AN15     | I   | F            | Analog input pins. The pin to be subject to conversion<br>is selected by the command input through the SIN pin.<br>Also, a series of pins from AN16 to AN23 can be used                                                                                                                                                                                                                                                                                               |

| 25 to 18 | 33 to 31,<br>29 to 25            | AN16 to<br>AN23 |     | G            | as a port input.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

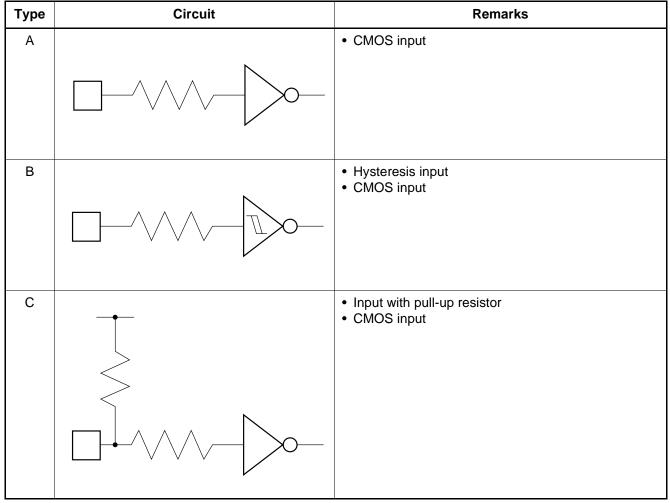

| 12       | 19                               | MOD             | Ι   | A            | Pin for selecting a serial data output mode:<br>"L": Mode A for output from the SOT pin in<br>synchronization with the fall of the SCK signal.<br>"H": Mode B for output from the SOT pin in<br>synchronization with the rise of the SCK signal.                                                                                                                                                                                                                      |

| 11<br>10 | 17<br>16                         | CS1<br>CS2X     | I   | A            | Input pins for selecting an extended serial interface<br>mode.<br>Setting the CS1 level to "H" and the CS2X level to "L"<br>enables A/D converted data transfer. Setting the CS1<br>level to "L" or the CS2X level to "H" clears the register<br>command without affecting A/D conversion. Serial<br>data input to the external extended serial input pin<br>ESIN is output to the SOT pin as it is. (See Section 7<br>"Extended Serial Interface" in "■ OPERATION.") |

| 4        | 10                               | SIN             | Ι   | В            | Serial data input pin<br>This pin is a hysteresis input with a filter.                                                                                                                                                                                                                                                                                                                                                                                                |

| 6        | 12                               | SOT             | 0   | н            | Serial data output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3        | 9                                | CCLK            | Ι   | В            | System clock input pin<br>This pin is a hysteresis input.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2        | 8                                | SCK             | Ι   | В            | Serial data transfer clock input pin<br>This pin is a hysteresis input with a filter.                                                                                                                                                                                                                                                                                                                                                                                 |

| 9        | 15                               | ATGX            | Ι   | С            | External trigger input pin. This pin incorporates a pull-<br>up resistor. The ATC command initiates A/D conversion<br>at the rise of the signal at this pin.<br>The pin is a hysteresis input.                                                                                                                                                                                                                                                                        |

| 8        | 14                               | IRQX            | 0   | Н            | A/D conversion interrupt signal input pin. The signal level becomes "L" upon completion of A/D conversion; it becomes "H" upon reception of data to be converted.                                                                                                                                                                                                                                                                                                     |

| 7        | 13                               | ENDC            | 0   | Н            | A/D conversion completion signal output pin. The signal level becomes "H" upon completion of A/D conversion; it becomes "L" upon reception of data to be converted.                                                                                                                                                                                                                                                                                                   |

| 5        | 11                               | ESIN            | Ι   | A            | Serial input extension input pin. When the CS1 level is<br>"L" or the CS2X level is "H," data input to the ESIN pin<br>is output to the SOT pin as it is.                                                                                                                                                                                                                                                                                                             |

| 1        | 7                                | RSTX            | I   | D            | Reset signal input pin. This pin incorporates a pull-up resistor. Setting the signal level to "L" initializes the internal circuit of the device. This pin is a hysteresis input with a filter.                                                                                                                                                                                                                                                                       |

(Continued)

| Pin | no.                     | Symbol | I/O | Circuit type | Deservitions                                                                                                 |

|-----|-------------------------|--------|-----|--------------|--------------------------------------------------------------------------------------------------------------|

| QFP | DIP                     | Symbol | 1/0 | Circuit type | Descriptions                                                                                                 |

| 14  | 21                      | TESTI  | I   | E            | Test input pin. This pin incorporates a pull-down resistor. Maintain the pin at "L" level during normal use. |

| 44  | 5                       | Vcc    | —   | _            | Digital circuit power supply pin                                                                             |

| 15  | 22                      | Vss    | —   | —            | Digital circuit ground pin                                                                                   |

| 43  | 4                       | AVcc   | —   | _            | Analog circuit power supply pin                                                                              |

| 17  | 24                      | AGND   | —   | —            | Analog circuit ground pin                                                                                    |

| 42  | 3                       | AVRH   | —   | —            | Reference (high) voltage input pin                                                                           |

| 16  | 23                      | AVRL   | —   | —            | Reference (low) voltage input pin                                                                            |

| 13  | 6, 18,<br>20, 30,<br>42 | N.C.   |     |              | Non-connection pin                                                                                           |

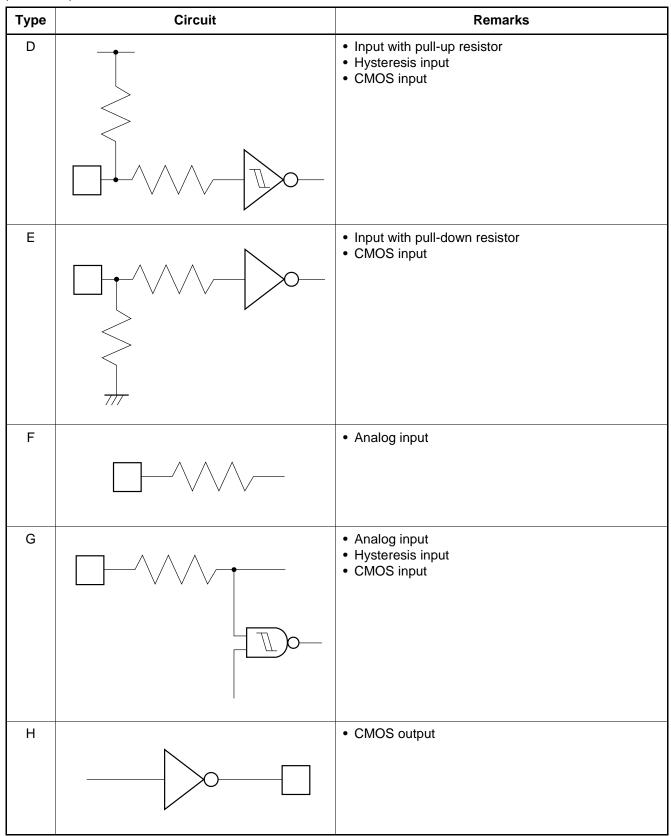

# ■ I/O CIRCUIT TYPE

(Continued)

(Continued)

# ■ BLOCK DIAGRAM

# ■ FUNCTIONAL DESCRIPTION

#### 1. SC (Serial Command) Register (Reset status: 0000H)

The SC register contains an A/D converter command and an input channel identification. Accessing this register after releasing it from the reset status activates the A/D converter.

Note that this register accepts setting even during A/D conversion.

Note also that input of a command to the register must take an interval of at least 4 CCLKs after input of the previous command.

| MSI | В               |    |    |    |    |    |    |    |    |    |       |      |    |    | LSB |

|-----|-----------------|----|----|----|----|----|----|----|----|----|-------|------|----|----|-----|

| bf  | be              | bd | bc | bb | ba | b9 | b8 | b7 | b6 | b5 | b4    | b3   | b2 | b1 | b0  |

| Co  | Command Channel |    |    |    |    |    |    |    |    |    | Don't | care |    |    |     |

#### (1) Command bits

A string of command bits selects an A/D converter command such as STOP. Setting a command during execution of another command cancels the command currently being executed.

| bf | be | bd | Command name | Function                                                                                                                                                                                                                                     |

|----|----|----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | 0  | STOP         | Stops A/D conversion (if it is being executed) and initializes the A/D converter. This command has the same effect as RSTX.                                                                                                                  |

| 0  | 0  | 1  | STC          | Executes A/D conversion of the specified channel once.<br>(See Section 3 "STC (Standard Conversion) Command.")                                                                                                                               |

| 0  | 1  | 0  | _            | Unused (*)                                                                                                                                                                                                                                   |

| 0  | 1  | 1  |              | Unused (*)                                                                                                                                                                                                                                   |

| 1  | 0  | 0  | NOP          | No-op command. Input of this command during A/D conversion does not affect operation. If followed by this command, the ATC command can transfer converted data while holding the NOP command.                                                |

| 1  | 0  | 1  | ATC          | The basic operation of this command is the same as that<br>of the STC command. The ATC command can leave the<br>A/D conversion start timing to the external trigger pin<br>ATGX. (See Section 4 "ATC (Auto Trigger Conversion)<br>Command.") |

| 1  | 1  | 0  | _            | Unused (*)                                                                                                                                                                                                                                   |

| 1  | 1  | 1  | —            | Unused (*)                                                                                                                                                                                                                                   |

\* : These command settings cause the STOP command to be executed.

#### (2) Channel select bits

A string of channel select bits selects the pin to be subject to A/D conversion. This bit string is enabled only for the STC or ATC command.

| bc | bb | ba | b9 | b8 | Pin to be selected | bc | bb | ba | b9 | b8 | Pin to be selected           |

|----|----|----|----|----|--------------------|----|----|----|----|----|------------------------------|

| 0  | 0  | 0  | 0  | 0  | AN0                | 1  | 0  | 0  | 0  | 0  | AN16                         |

| 0  | 0  | 0  | 0  | 1  | AN1                | :  | ÷  | ÷  | :  | :  | :                            |

| 0  | 0  | 0  | 1  | 0  | AN2                | 1  | 0  | 1  | 1  | 1  | AN23                         |

| 0  | 0  | 0  | 1  | 1  | AN3                | 1  | 1  | 0  | 0  | 0  |                              |

| 0  | 0  | 1  | 0  | 0  | AN4                | 1  | 1  | 0  | 0  | 1  |                              |

| :  | ÷  | ÷  | ÷  | :  | ÷                  | 1  | 1  | 0  | 1  | 0  |                              |

| 0  | 1  | 0  | 1  | 1  | AN11               | 1  | 1  | 0  | 1  | 1  | Undefined (*1)               |

| 0  | 1  | 1  | 0  | 0  | AN12               | 1  | 1  | 1  | 0  | 0  |                              |

| 0  | 1  | 1  | 0  | 1  | AN13               | 1  | 1  | 1  | 0  | 1  |                              |

| 0  | 1  | 1  | 1  | 0  | AN14               | 1  | 1  | 1  | 1  | 0  |                              |

| 0  | 1  | 1  | 1  | 1  | AN15               | 1  | 1  | 1  | 1  | 1  | Port input AN16 to AN23 (*2) |

\*1: These settings of the bit string cause the STOP command to be executed.

\*2: This setting is enabled only for the STC command. (See Section 5 "Port Input Command.") If this setting is made for the ATC command, the STOP command is executed.

#### 2. Data Output Format

Upon completion of A/D conversion, the ENDC pin level becomes "H" and the IRQX pin level becomes "L." Execution of serial transfer at this time outputs data in the format illustrated below. The data output timing can be selected by the MOD pin between the falling edge (mode A) or rising edge (mode B) of the SCK signal. When the ENDC pin level is "L," 0000H is output.

| MS | MSB LSB                               |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|----|---------------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Bf | Be                                    | Bd | Вс | Bb | Ва | B9 | B8 | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

|    | Converted data ENDC A/D converted pin |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

ENDC (A/D conversion completion flag): This bit is set to "1" upon completion of A/D conversion. It is set to "0" upon completion of serial transfer.

Note: SCK input upon low-to-high transition of the ENDC pin level should be avoided. Otherwise, data may not be output correctly.

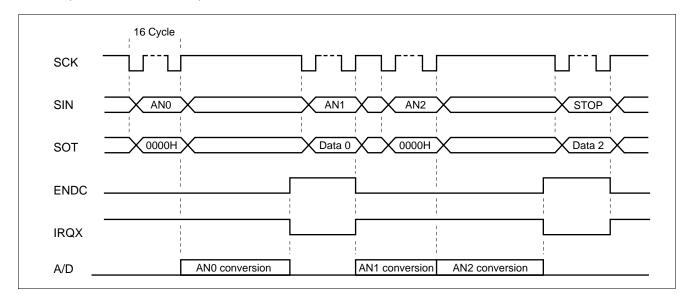

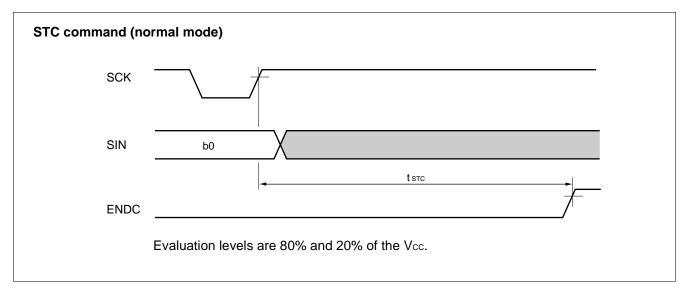

# 3. STC (Standard Conversion) Command

Input of the STC command executes A/D conversion of the specified channel once.

Impletion of A/D conversion, the ENDC signal rises while the IRQX signal falls. Clock input to the SCK pin after A/D conversion outputs data to the SOT pin. Upon completion of data output, the ENDC signal falls while the IRQX signal rises. If the next command is STOP or NOP, the A/D conversion is terminated. If the STC command is input during A/D conversion, the command currently being executed is cancelled and the STC command is executed.

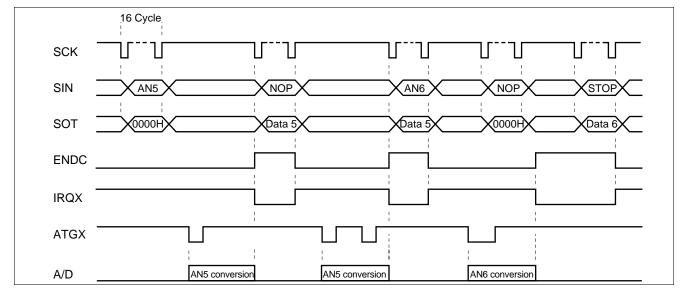

#### • Example of STC command execution (1)

STC command input during A/D conversion cancels the current command and executes A/D conversion of the new specified channel. Output data at this time is 0000H.

#### • Example of STC command execution (2)

NOP command input during A/D conversion does not affect operation. Output data at this time is 0000H. If A/ D conversion is completed during NOP command input, the ENDC and IRQX pin levels become "H" and "L" respectively upon completion of the NOP command input.

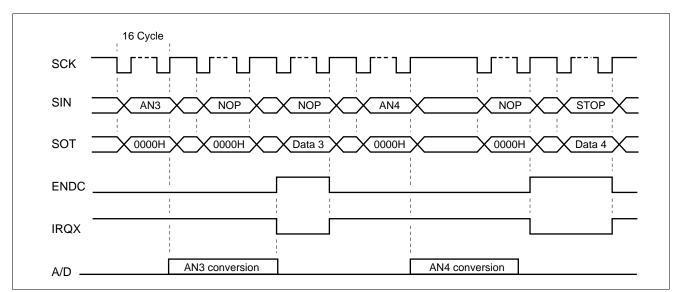

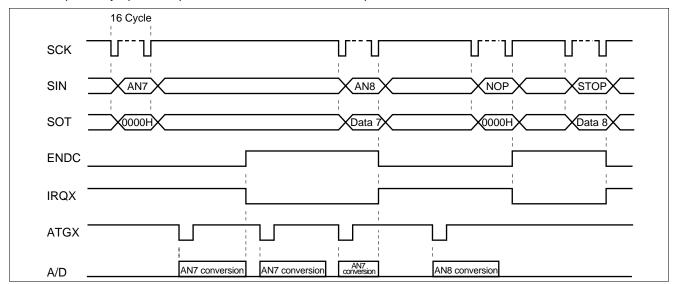

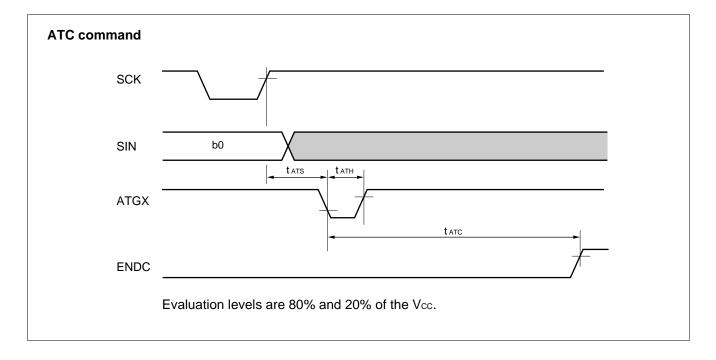

#### 4. ATC (Auto Trigger Conversion) Command

The ATC command is the same as the STC command in basic operation. This command can initiates A/D conversion using the external trigger pin ATGX. The external trigger signal is sampled by 1  $\mu$ s clock and filtered by 1 clock. The external trigger signal input during A/D conversion is ignored. If the next command is the STOP command, A/D conversion is terminated. If it is the NOP command, the ATC command is executed continuously. The channel cannot be changed at this time. To change the channel, input the ATC command to that effect.

#### • Example of ATC command execution (1)

NOP command input during A/D conversion enables the same channel to be A/D converted. An attempt to set the ATGX signal low during A/D conversion is ignored.

NOP command input during A/D conversion does not affect operation. Output data at this time is 0000H.

#### • Example of ATC command execution (2)

Setting the ATGX signal low again after A/D conversion restarts A/D conversion.

In data output mode B, however, do not use the ATC command in this way, or data will not be output correctly. If A/D conversion is completed during NOP command input, the ENDC and IRQX pin levels become "H" and "L" respectively upon completion of the NOP command input.

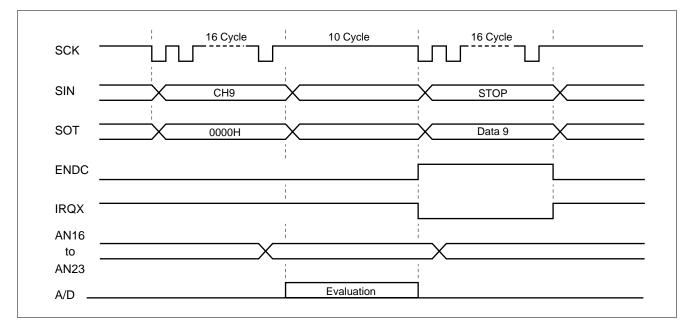

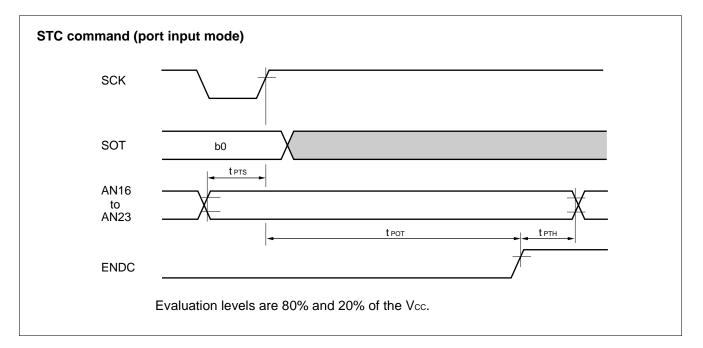

### 5. Port Input Command

The port input command executes I/O evaluation of 8-channel inputs from the AN16 to AN23 pins at a prescribed threshold in 10 clock cycles and outputs the results as port input data. The processing sequence is activated each time port input is selected by the STC command. Port input data is output in the following format:

| MSI | MSB LSB                                                                                                                                                                 |  |  |  |  |  |    |    |      |  |  |     |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|----|----|------|--|--|-----|--|--|

| Bf  | Bf         Be         Bd         Bc         Bb         Ba         B9         B8         B7         B6         B5         B4         B3         B2         B1         B0 |  |  |  |  |  |    |    |      |  |  |     |  |  |

|     | Evaluation data                                                                                                                                                         |  |  |  |  |  | "( | )" | ENDC |  |  | "1" |  |  |

#### Evaluation data:

The evaluation values of AN23 to AN16 are output to bits Bf to B8.

Evaluation value "H": Vin  $\ge 0.8 \text{ x Vcc}$ "L": Vin  $\le 0.2 \text{ x Vcc}$

ENDC (A/D completion flag):

This bit is set to "1" upon completion of A/D conversion. It is set to "0" upon completion of serial transfer.

#### • Example of STC command execution (3) (Port input command)

#### 6. Serial Output Select Function

The MB88111 can select the serial data output timing between the rising edge or falling edge of the clock signal according to the setting of the MOD pin.

| Mode A (MOD = "L")                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| scк — ЛЛЛЛЛЛЛЛЛЛЛЛЛЛЛЛЛ                                                                                                                                                                                                                                                                                                                                                        |

| MSB         LSB           SOT         Bf         Be         Bd         Bc         Bb         Ba         B9         B8         B7         B6         B5         B4         B3         B2         B1         B0           MSB         LSB                                                                                                                                        |

| SIN bf be bd bc bb ba b9 b8 b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                                                                                                                                                                                                            |

| Serial data is output at the falling edge of the SCK signal.                                                                                                                                                                                                                                                                                                                   |

| <ul> <li>Note: A/D converted data is not guaranteed if the MOD pin is switched when the ENDC signal is active. Before changing the output mode, make the ENDC inactive or set the RSTX pin level to "L" after switching the MOD pin.</li> <li>Mode B (MOD = "H")</li> </ul>                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                |

| MSB         LSB           SOT         Bf         Be         Bd         Bc         Bb         Ba         B9         B8         B7         B6         B5         B4         B3         B2         B1         B0                                                                                                                                                                  |

| MSB LSB<br>SIN bf be bd bc bb ba b9 b8 b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>Serial data is output at the rising edge of the SCK signal.</li> <li>Note: A/D converted data is not guaranteed if the MOD pin is switched when the ENDC signal is active. Before changing the output mode, make the ENDC inactive or set the RSTX pin level to "L" after switching the MOD pin. The first bit is output when the ENDC signal becomes "H."</li> </ul> |

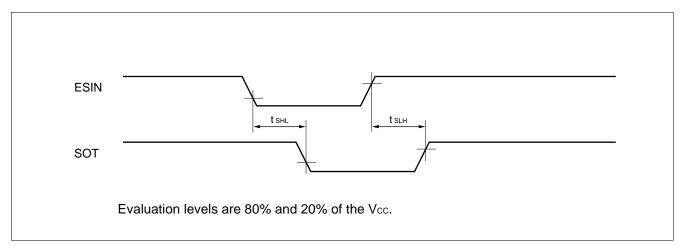

#### 7. Extended Serial Interface

The MB88111 can select whether to output A/D converted data or to output data input to the ESIN pin by controlling the CS1 and CS2X pins.

| CS1 | CS2X | SOT pin                    |

|-----|------|----------------------------|

| Н   | L    | A/D converted data         |

| L   | L    |                            |

| L   | Н    | Connection to the ESIN pin |

| Н   | Н    |                            |

Note: A/D converted data is not guaranteed if the CS1 or CS2X setting is changed during SCK input.

# ■ ELECTRICAL CHARACTERISTICS

# 1. Absolute Maximum Ratings

|                      |        |                              |      | (Vss=     | AGND = 0 \ |  |

|----------------------|--------|------------------------------|------|-----------|------------|--|

| Parameter            | Symbol | Conditions                   | Rat  | Ratings   |            |  |

| Falailletei          | Symbol | Conditions                   | Min. | Max.      | Unit       |  |

|                      | Vcc    |                              | -0.3 | +7.0      | V          |  |

| Power supply voltage | AVcc   |                              | -0.3 | +7.0*     | V          |  |

|                      | AVRH   | Based on Vss<br>(Ta = +25°C) | -0.3 | +7.0*     | V          |  |

| Input voltage        | Vin    | (14 - 120 0)                 | -0.3 | Vcc + 0.3 | V          |  |

| Output voltage       | Vout   |                              | -0.3 | Vcc + 0.3 | V          |  |

| Power consumption    | PD     |                              | _    | 150       | mW         |  |

| Storage temperature  | Tstg   | —                            | -55  | +150      | °C         |  |

\* :  $V_{CC} \ge AV_{CC} \ge AVRH$

# 2. Recommended Operating Conditions

| Parameter             | Symbol      | Val            | ues            | Unit |

|-----------------------|-------------|----------------|----------------|------|

| Falailletei           | Symbol      | Min.           | Max.           | Onit |

|                       | Vcc<br>AVcc | 3.5*           | 5.5*           | V    |

| Power supply voltage  | Vcc<br>AGND | 0              | 0              | V    |

|                       | AVRH        | AVcc 	imes 0.8 | AVcc           | V    |

|                       | AVRL        | 0              | AVcc 	imes 0.2 | V    |

| Operation temperature | Та          | -40            | +105           | °C   |

\* : Vcc  $\geq$  AVcc  $\geq$  AVRH

## 3. DC Characteristics

#### (1) Digital section

| Parameter                           | Pin name                                                 | Symbol | Conditions                                                   |          | Value |         | Unit |

|-------------------------------------|----------------------------------------------------------|--------|--------------------------------------------------------------|----------|-------|---------|------|

| Parameter                           | Pin name                                                 | Symbol | Conditions                                                   | Min.     | Тур.  | Max.    | Unit |

| Power supply voltage                |                                                          | Vcc    | _                                                            | 3.5      | 5.0   | 5.5     | V    |

| Power supply current                | Vcc                                                      | Icc    | Operation at<br>CLK = 1 MHz<br>(with no load)                | _        | 0.5   | 1.5     | mA   |

| Low-level input leakage current     | MOD, CCLK<br>CS1, CS2X<br>SCK, ESIN<br>SIN               | lızl1  | VIN = VSS                                                    | -2       | _     | 2       | μA   |

|                                     | ATGX<br>RSTX                                             | IIZL2  | V <sub>IN</sub> = V <sub>SS</sub><br>V <sub>CC</sub> = 5.0 V | -200     | -100  | -50     | μA   |

| High-level input leakage<br>current | MOD, CCLK<br>CS1, CS2X<br>SCK, ESIN<br>SIN, ATGX<br>RSTX | lızl1  | VIN = Vcc                                                    | -2       | _     | 2       | μΑ   |

|                                     | MOD, ESIN<br>CS1, CS2X                                   | VIL    | _                                                            | Vss-0.3  | _     | 0.3 Vcc | V    |

| Low-level input voltage             | SCK, CCLK<br>SIN, ATGX<br>RSTX, *                        | Vils   | _                                                            | Vss-0.3  | _     | 0.2 Vcc | V    |

|                                     | MOD, ESIN<br>CS1, CS2X                                   | Vін    | _                                                            | 0.7 Vcc  | _     | Vcc+0.3 | V    |

| High-level input voltage            | SCK, CCLK<br>SIN, ATGX<br>RSTX, *                        | Vihs   | _                                                            | 0.8 Vcc  | _     | Vcc+0.3 | V    |

| Hysteresis width                    | SCK, CCLK<br>SIN, ATGX<br>RSTX, *                        | VHYS   | _                                                            | 0.02 Vcc | _     | 0.3 Vcc | V    |

| Low-level output voltage            | SOT                                                      | Vol    | lo∟ = 2.5 mA                                                 | —        | _     | 0.4     | V    |

| High-level output voltage           | - IRQX<br>ENDC                                           | Vон    | Іон = -400 μА                                                | Vcc-0.4  | _     | _       | V    |

\* : AN16 to AN23 (port input mode)

### (2) Analog section

| (AVcc, Vcc = +3.5 V to +5.5 V (Vcc ≥ AVcc), Vss = AGND = 0 V, Ta = -40°C to +105°C |             |        |              |          |      |          |      |

|------------------------------------------------------------------------------------|-------------|--------|--------------|----------|------|----------|------|

| Parameter                                                                          | Pin name    | Symbol | Conditions   | Value    |      |          | Unit |

|                                                                                    |             |        |              | Min.     | Тур. | Max.     | onit |

| Resolution                                                                         | AN0 to AN23 | —      | —            | —        | 10   |          | bits |

| Monotonic increase                                                                 |             |        | _            | _        | 10   |          | bits |

| Linearity error                                                                    |             |        | —            | _        | —    | ±1       | LSB  |

| Differential linearity error                                                       |             |        | —            | —        | -    | ±1       | LSB  |

| Full-scale transition error                                                        |             |        | —            | —        | _    | ±1/2     | LSB  |

| Zero-transition error                                                              |             |        |              | _        | _    | ±1/2     | LSB  |

| Total error                                                                        |             |        | _            | _        | _    | ±2       | LSB  |

| Conversion time                                                                    | —           | _      | CCLK = 1 MHz | —        | _    | 50       | μs   |

| Input clock frequency                                                              | CCLK        | _      | —            | 800      | 1000 | 1200     | KHz  |

| Supply current                                                                     | AVcc        | IA     | _            | _        | 3.0  | 6.0      | mA   |

| Reference voltage supply current                                                   | AVRH        | IR     | _            | _        | 150  | 300      | μA   |

| Analog reference voltage                                                           | AVRH        |        | _            | 0.8 AVcc |      | AVcc     | V    |

|                                                                                    | AVRL        |        | _            | 0        |      | 0.2 AVcc | V    |

| Analog input voltage                                                               | AN0 to AN23 |        | _            | AVRL     |      | AVRH     | V    |

| Multiplexer OFF-leakage current                                                    |             | —      | —            | -200     |      | 200      | nA   |

• No missing code is guaranteed.

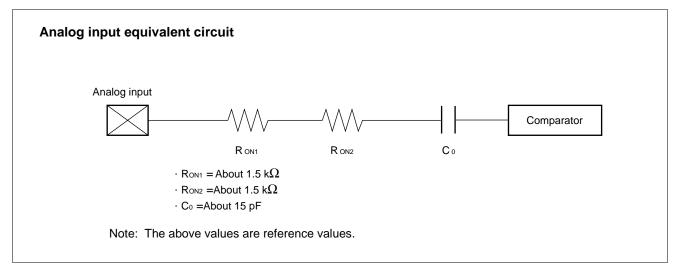

- Notes: If the output impedance of the external input is too high, the analog voltage sampling time may be insufficient.

- In the power-on sequence, turn the power supply for the digital system first before turning that for the analog system on.

# 4. AC Characteristics

| Porometer                                                                                                                                                                 | Curren al                       | O an dition a            | Values |      | 11   |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------|--------|------|------|--|

| Parameter                                                                                                                                                                 | Symbol                          | Conditions               | Min.   | Max. | Unit |  |

| CCLK clock cycle time                                                                                                                                                     | fськ                            | fclк = 1/fclк            | 800    | 1200 | KHz  |  |

| Low-level CCLK clock pulse width                                                                                                                                          | <b>t</b> cĸ∟                    | —                        | 400    | —    | ns   |  |

| High-level CCLK clock pulse width                                                                                                                                         | tскн                            | —                        | 400    | _    | ns   |  |

| CLK clock rise time tcr                                                                                                                                                   |                                 |                          | 10     |      |      |  |

| CCLK clock fall time                                                                                                                                                      | tcr                             |                          | _      | 10   | ns   |  |

| SCK clock cycle time                                                                                                                                                      | fscк                            | tscк = 1/fscк            | 400    | 1200 | KHz  |  |

| Low-level SCK clock pulse width                                                                                                                                           | <b>t</b> sĸ∟                    | —                        | 400    | —    | ns   |  |

| High-level SCK clock pulse width                                                                                                                                          | <b>t</b> sкн                    | —                        | 400    | —    | ns   |  |

| SCK clock rise time                                                                                                                                                       | tsr                             |                          |        | 10   | ns   |  |

| SCK clock fall time                                                                                                                                                       | tsr                             |                          | _      |      |      |  |

| SIN setup time                                                                                                                                                            | tsis                            | _                        | 50     | _    | ns   |  |

| SIN hold time                                                                                                                                                             | d time tsin —                   |                          | 250    | _    | ns   |  |

| Command interval                                                                                                                                                          | tсом                            | CCLK = 1 MHz             | 4      | _    | μs   |  |

| ENDC reset time                                                                                                                                                           | tenr                            | R See "Load conditions." |        | 1    | μs   |  |

| RSTX pulse width                                                                                                                                                          | trsн                            | _                        | 100    | _    | ns   |  |

| $RSTX \uparrow \to SCK \downarrow time$                                                                                                                                   | trss                            |                          | 1      | _    | μs   |  |

| $\begin{array}{rcl} SCK & \uparrow \to & CS1 \downarrow time \\ SCK & \uparrow \to & CS2X \uparrow time \end{array}$                                                      | tcss                            | _                        | 500    | _    | ns   |  |

| $\begin{array}{l} \text{CS1} \uparrow \rightarrow \text{SCK} \downarrow \text{time} \\ \text{CS2X} \downarrow \rightarrow  \text{SCK} \downarrow \text{time} \end{array}$ | tсsн                            | _                        | 500    | _    | ns   |  |

| SOT output delay time (mode A)                                                                                                                                            | <b>t</b> soda                   | See "Load conditions."   | —      | 300  | ns   |  |

| SOT output delay time (mode B)                                                                                                                                            | B) tsodb See "Load conditions." |                          | _      | 300  | ns   |  |

| ENDC $\uparrow \rightarrow$ SOT output (mode B)                                                                                                                           | tsoнв                           | See "Load conditions."   | _      | 200  | ns   |  |

| STC command A/D conversion time                                                                                                                                           | tstc                            | CCLK = 1 MHz             | —      | 50   | μs   |  |

| ATC command A/D conversion time                                                                                                                                           | <b>t</b> SATC                   | CCLK = 1 MHz             |        | 50   | μs   |  |

| ATGX setup time                                                                                                                                                           | <b>t</b> sats                   | CCLK = 1 MHz             | 4      |      | μs   |  |

| ATGX hold time                                                                                                                                                            | <b>t</b> sath                   | CCLK = 1 MHz             | 2      |      | μs   |  |

| Port input evaluation time                                                                                                                                                | tрот                            | CCLK = 1 MHz             |        | 10   | μs   |  |

| Port input setup time                                                                                                                                                     | <b>t</b> PTS                    |                          | 0      |      | ns   |  |

| Port input hold time                                                                                                                                                      | <b>t</b> PTH                    | _                        | 0      |      | ns   |  |

| Extended serial HL propagation delay                                                                                                                                      | <b>t</b> shl                    | See "Load conditions."   |        | 100  | ns   |  |

| Extended serial LH propagation delay                                                                                                                                      | <b>t</b> s∟н                    | See "Load conditions."   | _      | 100  | ns   |  |

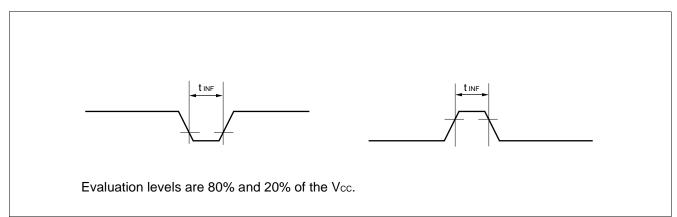

| Noise filter width                                                                                                                                                        | tinf                            | _                        | 15     |      | ns   |  |

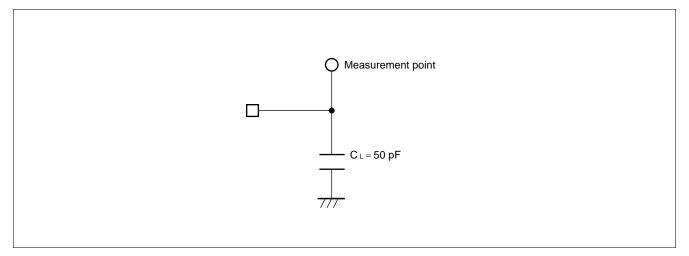

# **AC Test Condition**

# ■ TIMING DIAGRAM

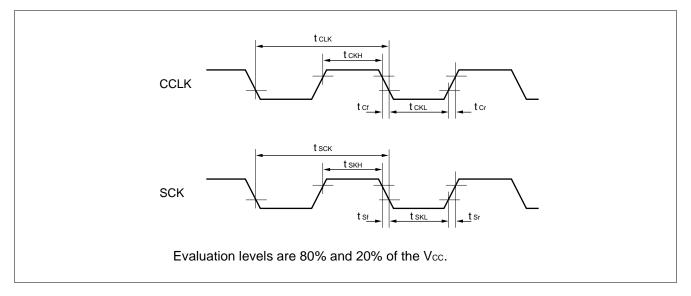

# 1. Input Clock Timing

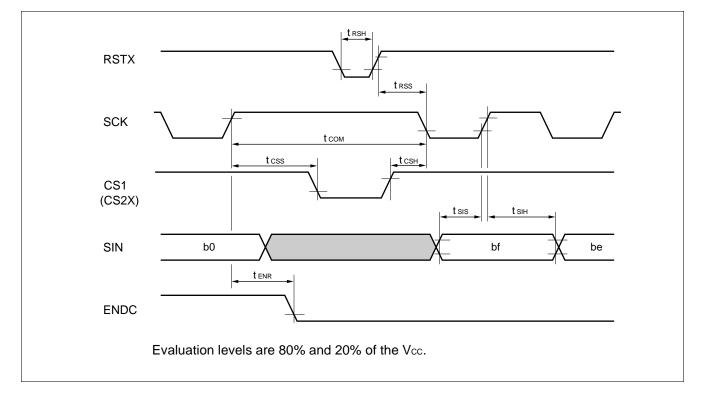

# 2. Serial Data Input Timing

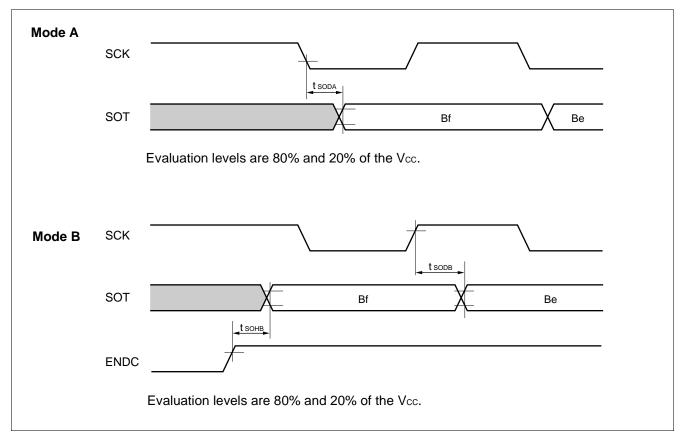

# 3. Serial Data Output Timing

## 4. A/D Conversion and Port Input Evaluation

# 5. Extended Serial Interface

#### 6. Noise Filter

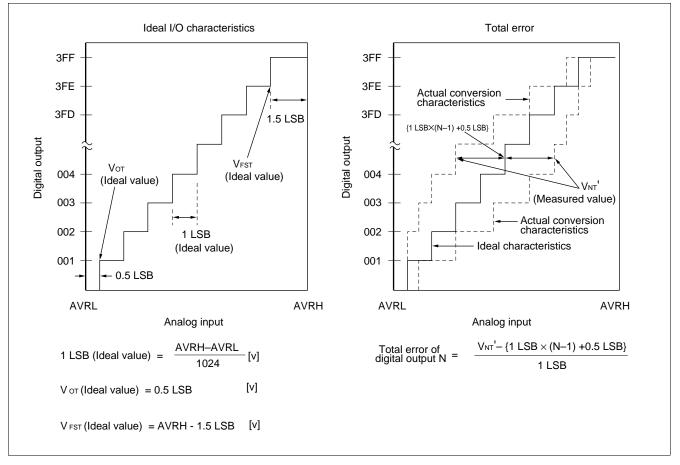

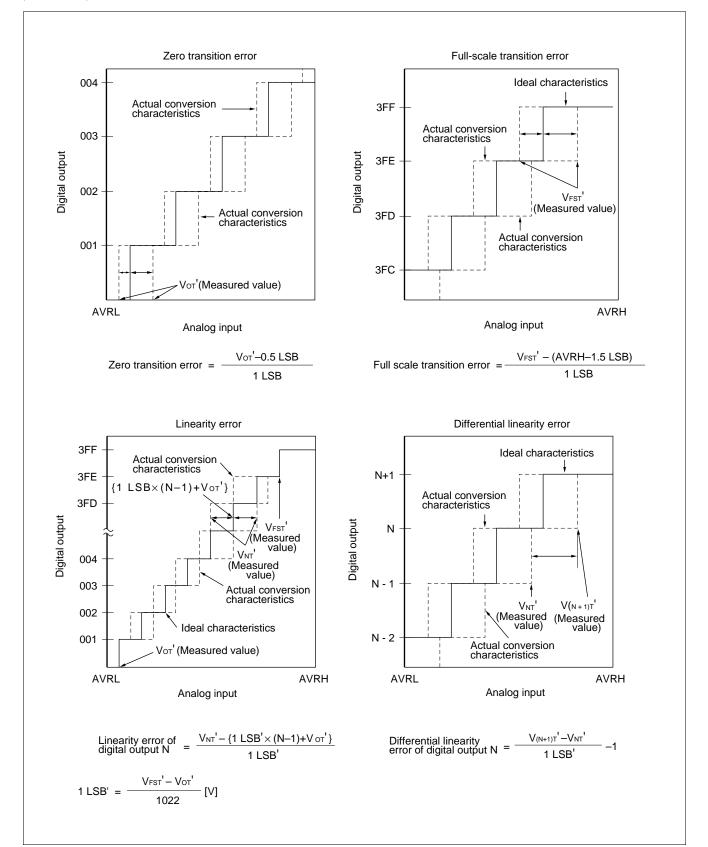

# DEFINITIONS OF A/D CONVERTER TERMS

Resolution

Analog transition identifiable by the A/D converter

• Linearity error

Deviation of the straight line drawn between the zero transition point (00 0000 0000  $\leftrightarrow$  00 0000 0001) and the full-scale transition point (11 1111 1110  $\leftrightarrow$  11 1111 1111) of the device from actual conversion characteristics

Differential linearity error

Deviation from the ideal input voltage required to shift output code by one LSB

• Total error

Difference between actual and logical values. This error is caused by a zero transition error, full-scale transition error, linearity error, quantum error, and by noise.

(Continued)

#### (Continued)

# ORDERING INFORMATION

| Part number | Package                                 | Remarks |

|-------------|-----------------------------------------|---------|

| MB88111PFQ  | 44-pin, Plastic QFP<br>(FPT-44P-M11)    |         |

| MB88111P-SH | 48-pin, Plastic SH-DIP<br>(DIP-48P-M01) |         |

### ■ PACKAGE DIMENSIONS

# FUJITSU LIMITED

#### All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

F9703 © FUJITSU LIMITED Printed in Japan